A 212MPixels/s 4096x2160p Multiview Video Encoder Chip for 3D/Quad HDTV Applications

Abstract

A 4096x2160p multiview video encoder chip is implemented on a 11.46mm2 die in 90nm CMOS. An 8-stage macroblock pipelined architecture with cache-based prediction core achieves 212Mpixels/s throughput, which is 3.4x to 7.7x higher than the previous works. The 407Mpixels/W power efficiency is achieved, and 94% on-chip SRAM size and 79% external memory bandwidth are saved.

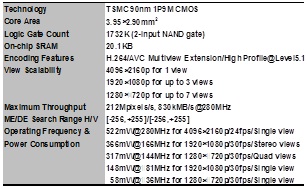

Chip Spec

|

|

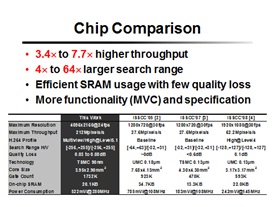

Comparison

|

|