Student ID\_\_\_\_\_

Department/Year\_\_\_\_\_

# **Mid-term Examination**

Introduction to Computer Science Class#: 901 10110, Session#: 03 Spring 2005

> 15:40-17:20 Wednesday April 20, 2005

### Prohibited

- 1. You are not allowed to write down the answers using pencils. Use only black- or blue-inked pens.

- 2. You are not allowed to read books or any references not on the question sheets.

- 3. You are not allowed to use calculators or electronic devices in any form.

- 4. You are not allowed to use extra sheets of papers.

- 5. You are not allowed to have any oral, visual, gesture exchange about the exam questions or answers during the exam.

#### Cautions

- 1. Check if you get 11 pages (including this title page), 19 questions.

- 2. Write your name (in Chinese), student ID, and department/year down on top of the cover page.

- 3. You have 100 minutes to answer the questions. Skim through all questions and start from the questions you feel more confident with.

- 4. You are allowed to use only English to answer the questions. Please make sure your answers make sense.

- 5. If you have any extra-exam emergency or problem regarding the exam questions, raise your hand quietly. The exam administrator will approach you and deal with the problem.

## Appendix C

The following table is from Appendix C of the text. It is included here so that it can be incorporated in tests for student reference. Questions in this exam refer to this table as the "language description table."

### **Op-Code Operand Description**

| 1 | RXY | LOAD the register R with the bit pattern found in the memory cell whose address is XY. <i>Example:</i> 14A3 would cause the contents of the memory cell located at address A3 to be placed in register 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | RXY | LOAD the register R with the bit pattern XY. <i>Example:</i> 20A3 would cause the value A3 to be placed in register 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3 | RXY | STORE the bit pattern found in register R in the memory cell whose address is XY. <i>Example:</i> 35B1 would cause the contents of register 5 to be placed in the memory cell whose address is B1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4 | 0RS | MOVE the bit pattern found in register R to register S.<br><i>Example:</i> 40A4 would cause the contents of register A to be copied into register 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5 | RST | ADD the bit patterns in registers S and T as though they were two's complement representations and leave the result in register R. <i>Example:</i> 5726 would cause the binary values in registers 2 and 6 to be added and the sum placed in register 7.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6 | RST | ADD the bit patterns in registers S and T as though they represented values in floating-point notation and leave the floating-point result in register R. <i>Example:</i> 634E would cause the values in registers 4 and E to be added as floating-point values and the result to be placed in register 3.                                                                                                                                                                                                                                                                                                                                                                       |

| 7 | RST | OR the bit patterns in registers S and T and place the result in register R. <i>Example:</i> 7CB4 would cause the result of ORing the contents of registers B and 4 to be placed in register C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8 | RST | AND the bit patterns in register S and T and place the result in register R. <i>Example:</i> 8045 would cause the result of ANDing the contents of registers 4 and 5 to be placed in register 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9 | RST | EXCLUSIVE OR the bit patterns in registers S and T and place the result in register R. <i>Example:</i> 95F3 would cause the result of EXCLUSIVE ORing the contents of registers F and 3 to be placed in register 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A | R0X | ROTATE the bit pattern in register R one bit to the right X times. Each time place the bit that started at the low-order end at the high-order end. <i>Example:</i> A403 would cause the contents of register 4 to be rotated 3 bits to the right in a circular fashion.                                                                                                                                                                                                                                                                                                                                                                                                         |

| В | RXY | JUMP to the instruction located in the memory cell at address XY if the bit pattern in register R is equal to the bit pattern in register number 0. Otherwise, continue with the normal sequence of execution. (The jump is implemented by copying XY into the program counter during the execute phase.) <i>Example:</i> B43C would first compare the contents of register 4 with the contents of register 0. If the two were equal, the pattern 3C would be placed in the program counter so that the next instruction executed would be the one located at that memory address. Otherwise, nothing would be done and program execution would continue in its normal sequence. |

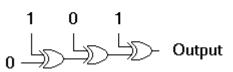

C 000 HALT execution. *Example:* C000 would cause program execution to stop. 1. (a) What is the output of the circuit below?

#### Input Pattern

(b). In general, how does the three-bit input pattern across the top of the diagram relate to the circuit's output?

#### ANSWER:

- (a) 0

- (b) The output is 0 if the input parity is odd; the output is 1 if the input parity is even.

2. (a) Represent the bit pattern 1011010010011111 in hexadecimal notation.(b) Convert the number A7DF in hexadecimal notation to its bit pattern.

ANSWER:

(a) B49F

(b) 1010 0111 1101 1111

3. Construct the entire two's complement scale in which each value is represented by three bits.

ANSWER:

| 3  | 011 |

|----|-----|

| 2  | 010 |

| 1  | 001 |

| 0  | 000 |

| -1 | 111 |

| -2 | 110 |

| -3 | 101 |

| -4 | 100 |

4. Which of the following bit patterns (represented in hexadecimal notation) represents a negative number in two's complement notation?

(a) 7F (b) 55 (c) A6 (d) 08

ANSWER: (c)

5. In which of the following addition problems (using two's complement notation) does an overflow error occur?

| (a) | 0011   | (b) | 0100   | (c) | 1100   |

|-----|--------|-----|--------|-----|--------|

|     | + 1010 |     | + 0100 | -   | + 1100 |

ANSWER: (b)

6. (a) Rewrite 2 1/4 (represented in base ten notation) in binary notation.

(b) Translate this binary representation 10.011 into its equivalent base ten representation

ANSWER: (a) 10.01 (b) 2 3/8

7. If the patterns 101.11 and 1.011 represent values in binary notation, what is the binary representation of their sum?

ANSWER: 111.001

8. Which of the following values cannot be stored accurately using a floating-point format in which the most significant bit is the sign bit, the next three bits represent the exponent field in excess notation, and the last four bits represent the mantissa?

(a) 2 1/2

(b) 3/16

(c) 7

(d) 6 1/4

ANSWER: (d)

9. The following is an error-correcting code in which any two patterns differ by a Hamming distance of at least three.

| Representation |  |

|----------------|--|

| 000000         |  |

| 001111         |  |

| 010011         |  |

| 011100         |  |

| 100110         |  |

| 101001         |  |

| 110101         |  |

| 111010         |  |

|                |  |

Decode each of the following patterns

- (a) 010011

- (b) 101010

- (c) 011000

- (d) 101101

ANSWER: C, H, D, F

10. The following message was compressed using LZ77.

1010101(4,3,1)(8,7,1)(16,8,0)(8,6,1)

- (a) How long was the original message?

- (b) Decompress the message

ANSWER:

(a) 35

(b) 1010101 0101 01010101 010101010 1010101

11. Encode each of the following commands in terms of the machine language described in the language description table.

(a) LOAD register 7 with the value A5.

(b) LOAD register 7 with the contents of the memory cell at address A5.

ANSWER: (a) 27A5 (b) 17A5

12. Decode each of the following instructions that were encoded using the language description table.

(a) 8023

(b) B288

ANSWER:

(a) AND the contents of registers 2 and 3, leaving the result in register 0.

(b) JUMP to the instruction at address 88 if the contents of register 2 equals that of register 0.

13. The following table shows a portion of a machine's memory containing a program written in the language described in the language description table. Answer the questions below assuming that the machine is started with its program counter containing 00.

| address | content | add | address |  |

|---------|---------|-----|---------|--|

| 00      | 25      | 07  | 00      |  |

| 01      | 03      | 08  | 34      |  |

| 02      | A5      | 09  | 04      |  |

| 03      | 02      | 0A  | в0      |  |

| 04      | 35      | 0B  | 03      |  |

| 05      | 03      | 0C  | C0      |  |

| 06      | 24      | 0D  | 00      |  |

|         |         |     |         |  |

(a) What value (in hexadecimal notion) will be in register 5 when the machine halts?(b) What value (in hexadecimal notion) will be in the program counter when the machine halts?

(c) What value (in hexadecimal notion) will be at memory location 04 when the machine halts?

ANSWER: (a) C0 (b) 05 (c) 00

14. Using the machine language described in the language description table, write a sequence of instructions that will subtract one from the value (represented in two's complement notation) stored at memory address A0.

ANSWER: 2XFF 1YA0 5YXY 3YA0 (where X and Y can be any distinct registers) 14. What is the difference between batch processing and interactive processing?

ANSWER: see exercise solution

15. What is the difference between a process that is waiting as opposed to a process that is ready?

ANSWER: see exercise solution

16. What is the difference between virtual memory and main memory?

ANSWER: see exercise solution

17. Explain why the average length of a time slice would be reduced if the processes in an operating system's process table perform lots of I/O operations.

ANSWER: Once a process requests an I/O operation, its time slice will be terminated, it will be labeled as a waiting process, and another process will be allowed to start another time slice. Thus, the first process's effective time slice would be reduced.

18. What problem arises as the lengths of the time slices in a time-sharing system are made shorter and shorter? What about as they become longer and longer?

ANSWER: see exercise solution

19. Suppose a password consisted of a string of 6 characters from the Arabic digits (10 characters). If each possible password could be tested in a millisecond, how many days would it take to test all possible passwords? If 5 wrong-password login errors are allowed per day, how many days would it take to test all possible passwords?

ANSWER: 5/432 200,000