Spring 2021

數位控制系統 Digital Control Systems

DCS-15 Timing Analysis

# Feng-Li Lian NTU-EE Feb – Jun, 2021

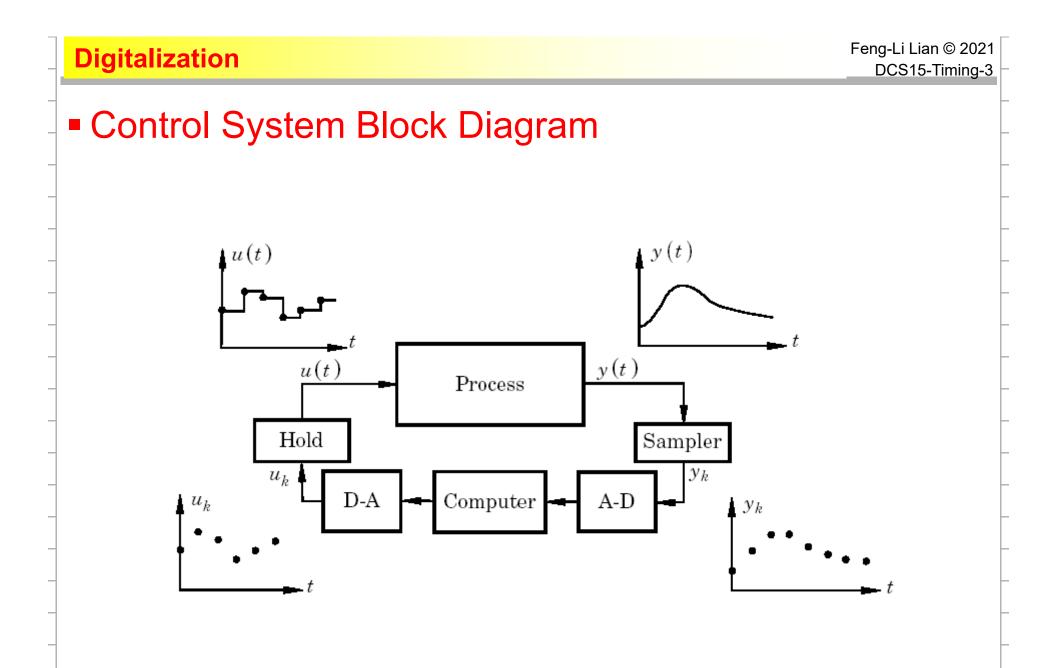

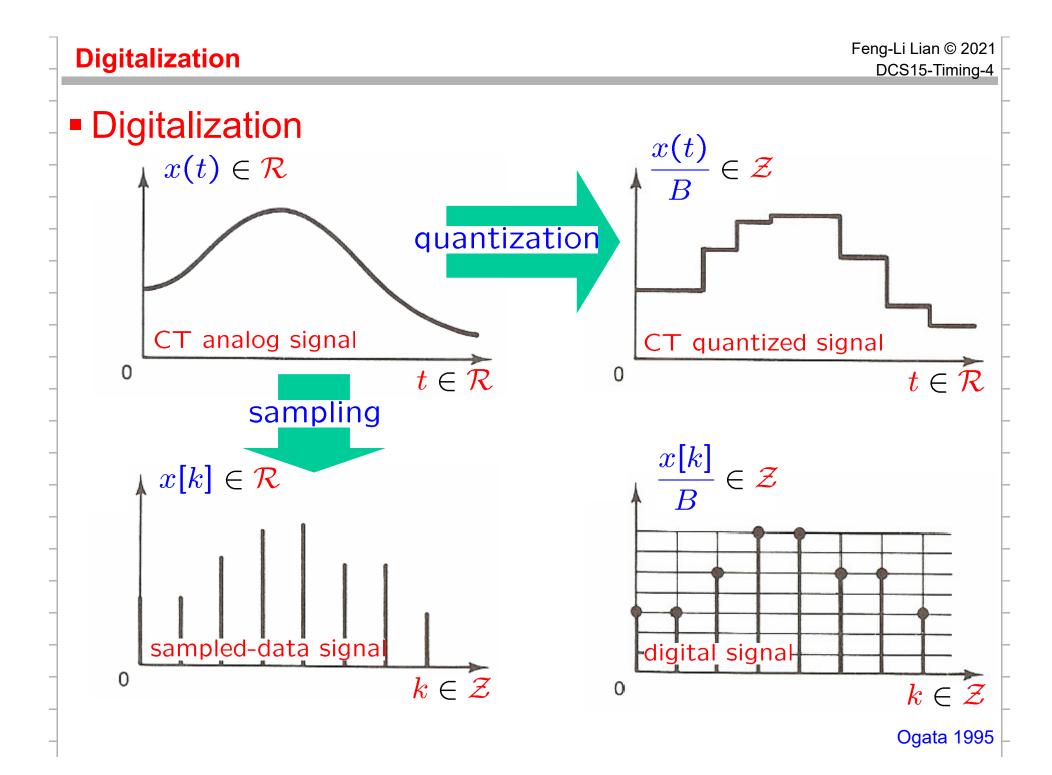

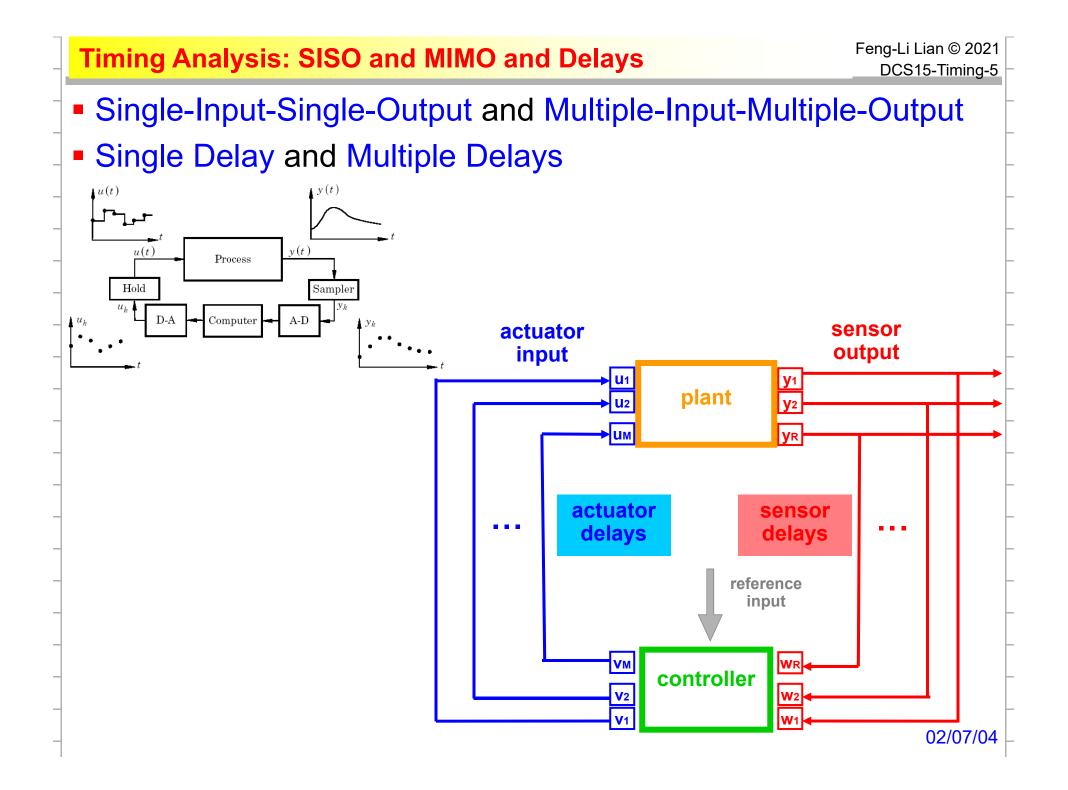

- Digitalization

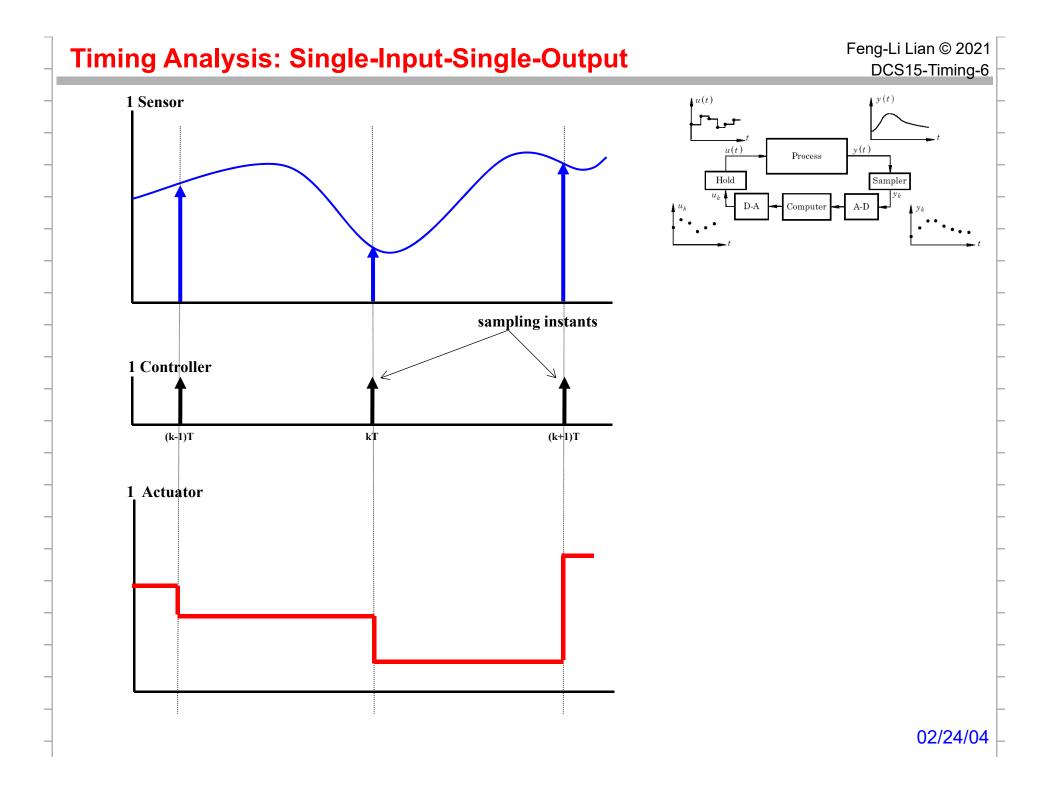

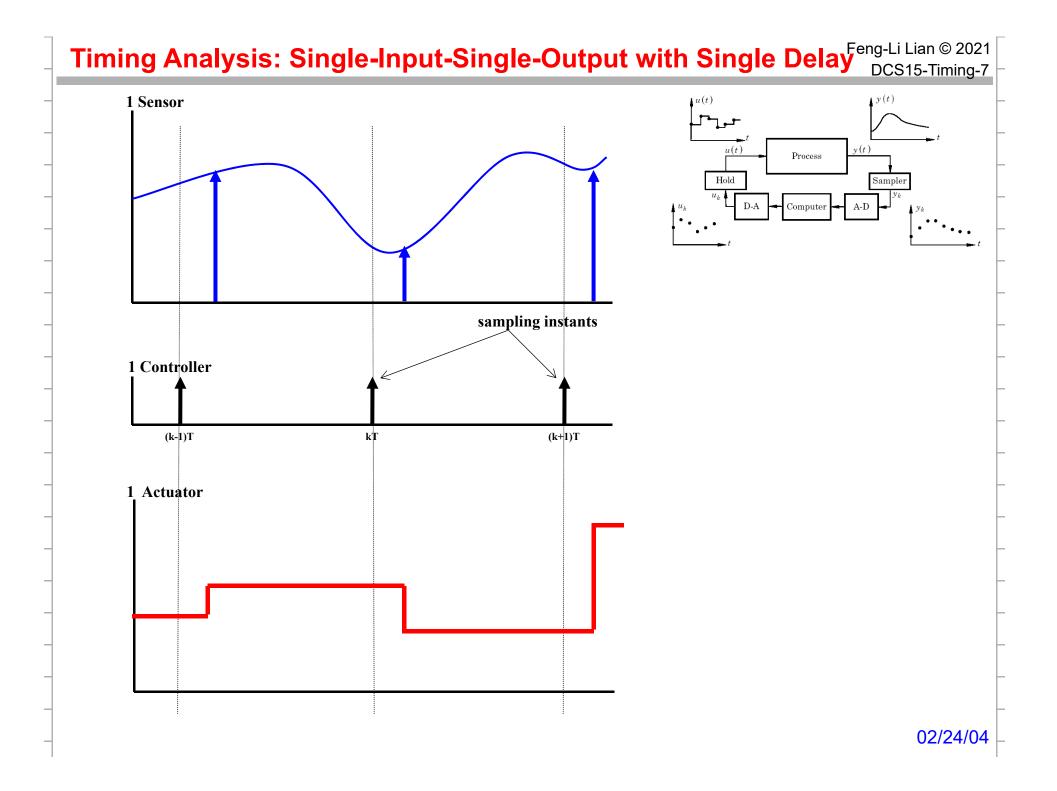

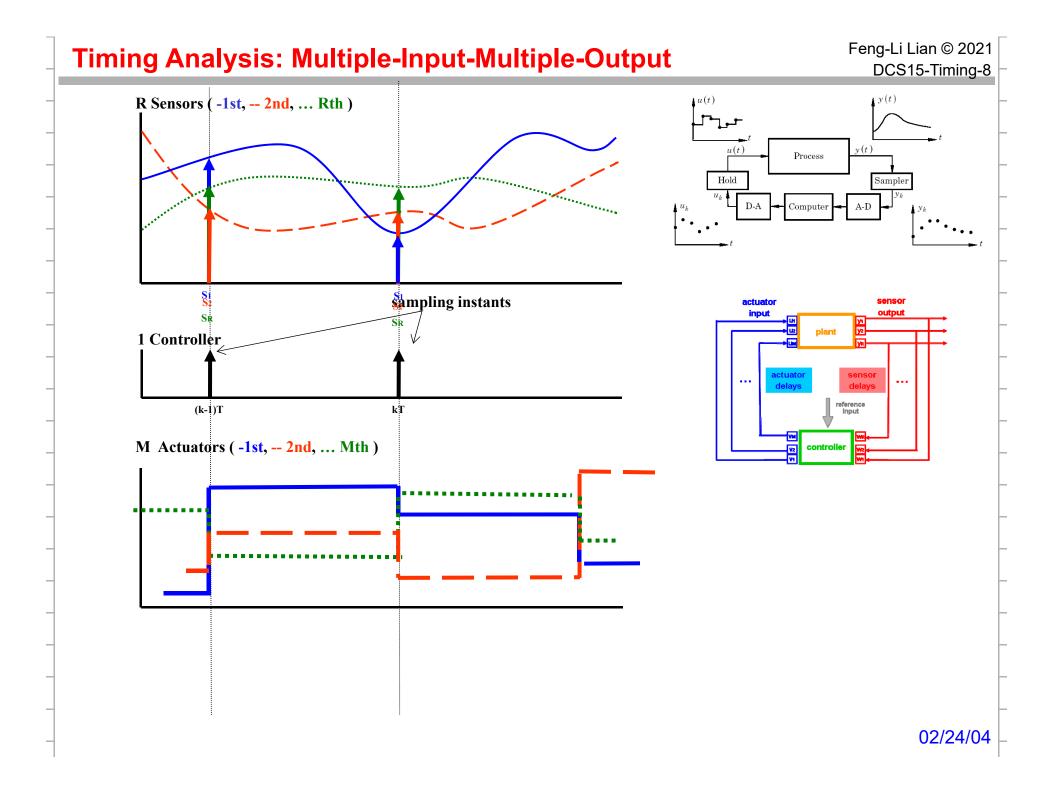

- Timing Analysis in a Control System

- Some Related Issues:

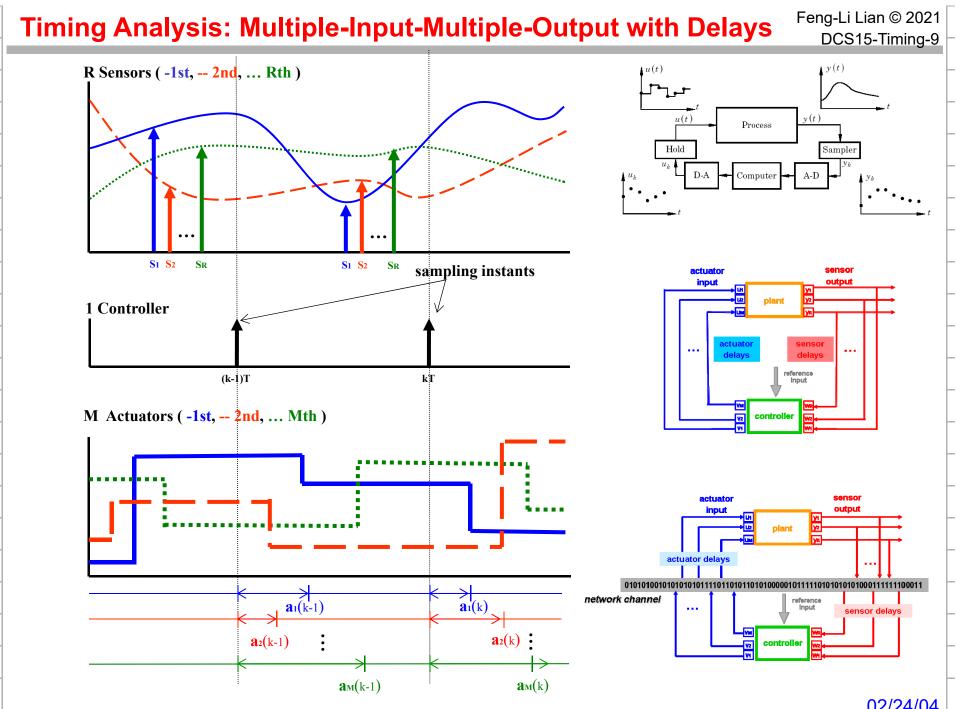

- Multiple or Random Time-Delay Systems

- Types of Jitters

- Timing Requirements & Control Attributes

- Multiprocessor Implementation of Digital Engine Control

- End-to-End Delay of Videoconferencing

- Timing Analysis for Programs

- Temporal Characteristics of Task Transmission

02/24/04

#### Paper:

- B. Wittenmark, J. Nilsson, and M. Torngren,

- "Timing problems in real-time control systems,"

- In Proceedings of American Control Conference, Seattle, Washington, pp. 2000–2004, June 1995.

## Abstract:

In this paper we have discussed some of the timing problems in real-time control systems. The influence of the scheduling on the models is discussed together with different interesting problem formulations. The effect of the timing problems are exemplified through some simulated examples. The future research will concentrate on analysis of the robustness properties with respect to time-delay variations and jitter in sampled-data systems. The following items will be of great interest: 1) Studying ways of analyzing timevarying systems, in particular influences of jitter and time-varying delays. 2) Applicability of robustness theory to derive jitter specifications. 3) Ways of detecting and compensating for transient errors.

#### Paper:

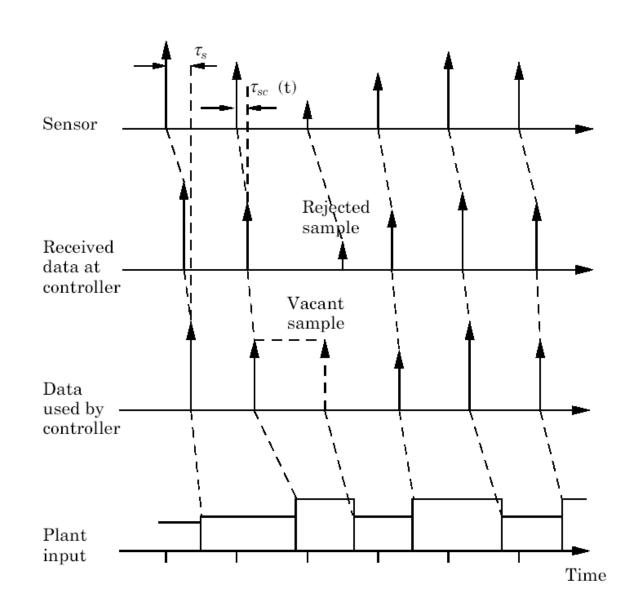

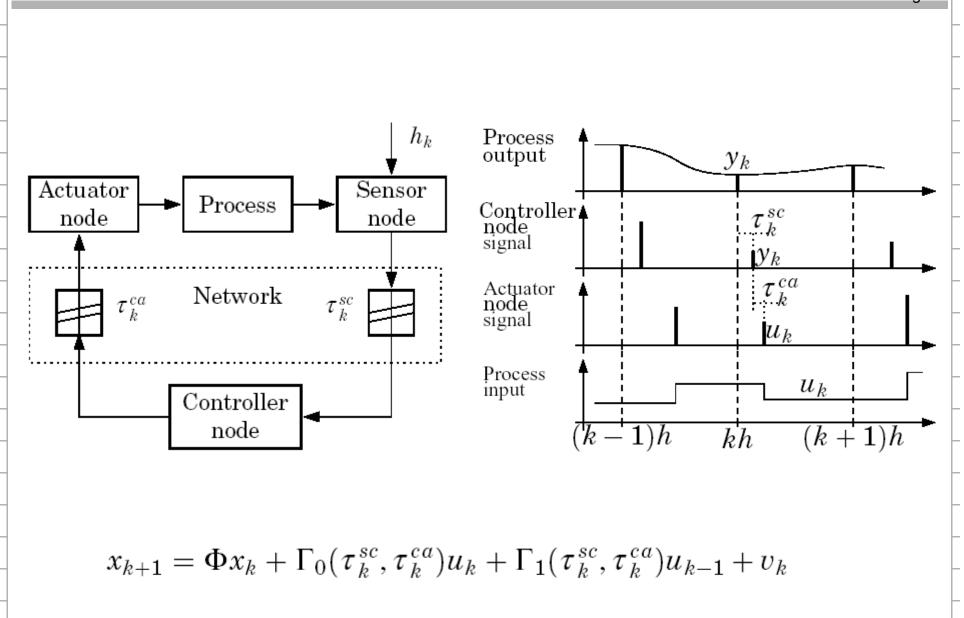

- J. Nilsson, B. Bernhardsson, B. Wittenmark,

- "Stochastic analysis and control of real-time systems with random time delays,"

- Automatica, 34(1):57-64, Jan. 1998.

# • Abstract:

The paper discusses modeling and analysis of real-time systems subject to random time delays in the communication network. A new method for analysis of different control schemes is presented. The method is used to evaluate different suggested schemes from the literature. A new scheme, using so called timestamps, for handling the random time delays is then developed and successfully compared with previous schemes. The new scheme is based on stochastic control theory and a separation property is shown to hold for the optimal controller.

Feng-Li Lian © 2021 DCS15-Timing-13

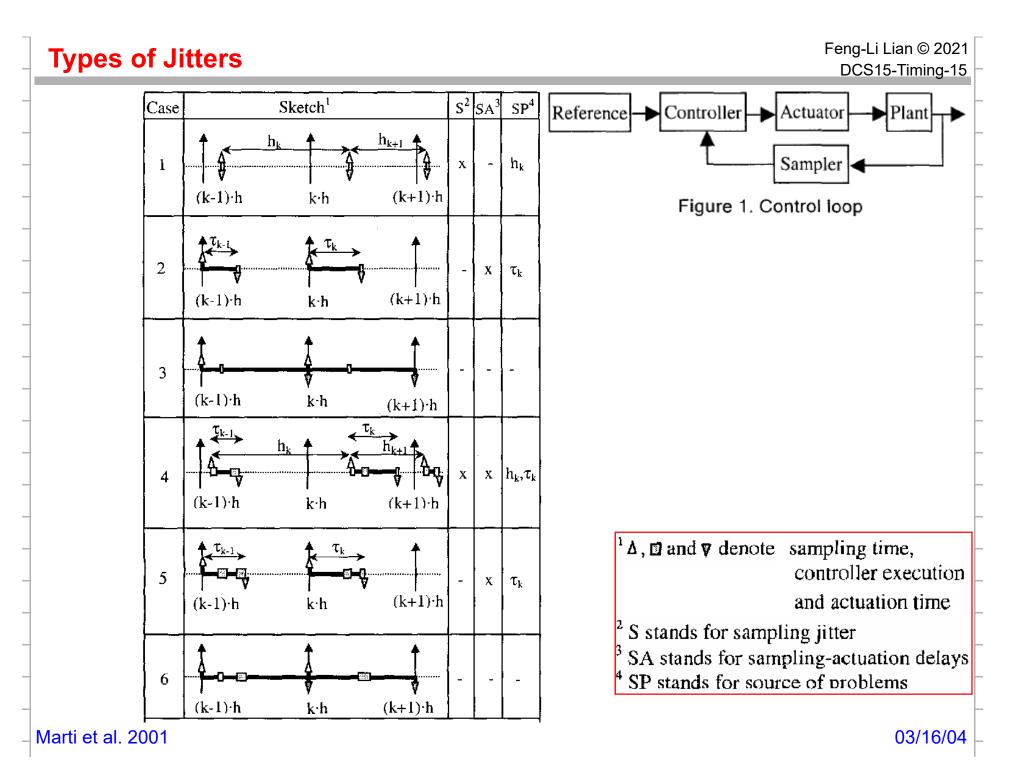

# **Types of Jitters**

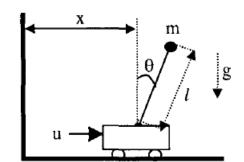

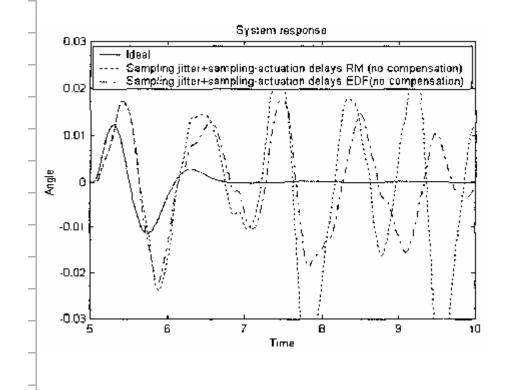

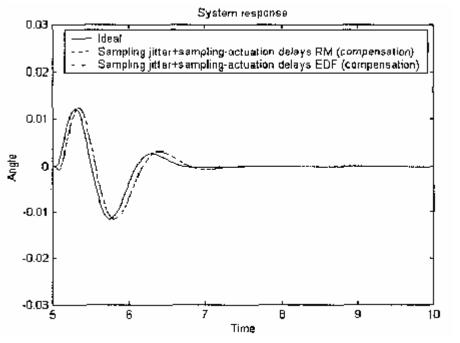

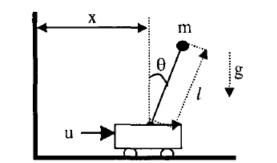

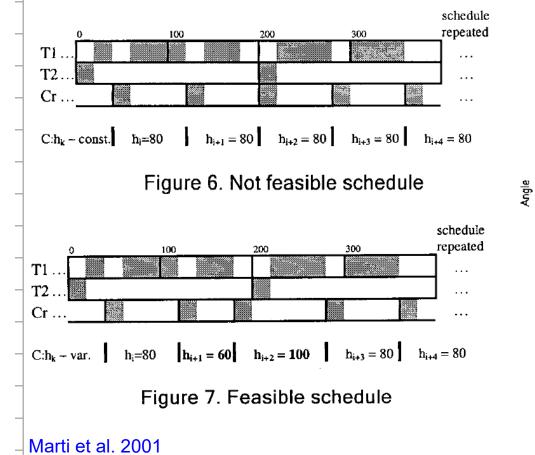

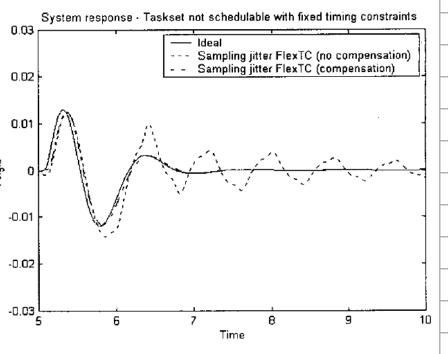

- P. Marti, J.M. Fuertes, G. Fohler, and K. Ramamritham,

- "Jitter compensation for real-time control systems,"

- In Proc. 22nd IEEE Real-Time Systems Symposium, pp. 39-48, Dec. 2001.

- Abstract:

- In this paper, we first identify the potential violations of control assumptions inherent in standard real-time scheduling approaches (because of the presence of jitters) that causes, degradation in control performance and may even lead to instability. We then develop practical approaches founded on control theory to deal with these violations. Our approach is based on the notion of compensations wherein controller parameters are adjusted at runtime for the presence of jitters. Through time and memory overhead analysis, and by elaborating on the implementation details, we characterize when offline and on-line compensations are feasible. Our experimental results confirm that our approach does compensate for the degraded control performance when EDF and FPS algorithms are used for scheduling the control tasks. Our compensation approach provides us another advantage that leads to better schedulability of control tasks. This derives from the potential to derive more flexible timing constraints, beyond periods and deadlines necessary to apply EDF and FPS. Overall, our approach provides guarantees offline that the control system will be stable at runtime-if temporal requirements are met at runtimeeven when actual execution patterns are not known beforehand. With our approach, we can address the problems due to (a) sampling jitters, (b) varying delays between sampling and actuation, or (c) both-not addressable using traditional EDF and FPS based scheduling, or by previous real-time and control integration approaches. 05/03/09

# **Types of Jitters: Fixed Timing Constraints**

Feng-Li Lian © 2021 DCS15-Timing-16

|   | Task1 | Task2 | Control task |

|---|-------|-------|--------------|

| Т | 60ms  | 70ms  | 80ms         |

| C | 10ms  | 10ms  | 1 ms         |

\_ Marti et al. 2001

### **Types of Jitters: Flexible Timing Constraints**

|                 | Т              | С    | DL   | Offset |

|-----------------|----------------|------|------|--------|

| Task T1         | 100ms          | 60ms |      |        |

| Task T2         | 200ms          | 20ms | 20ms |        |

| Control task Cr | h <sub>k</sub> | 20ms | 20ms | 40ms   |

03/21/05

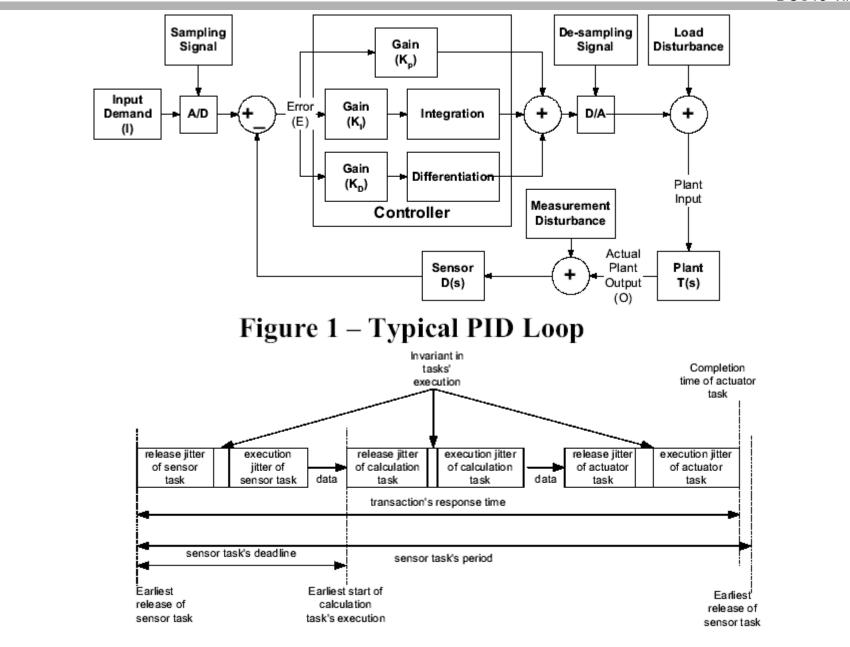

# **Timing Requirements & Control Attributes**

- I. Bate, P. Nightingale, and A. Cervin,

- "Establishing timing requirements and control attributes for control loops in real-time systems,"

- Proc. 15th Euromicro Conf. on Real-Time Systems, pp. 121-128, July 2003.

- Abstract:

- Advances in scheduling theory have given designers of control systems greater flexibility over their choice of timing requirements. This could lead to systems becoming more responsive, more flexible and more maintainable. However, experience has shown that engineers find it difficult to exploit these advantages due to the difficulty in determining the "real" timing requirements of systems and therefore the techniques have delivered less benefit than expected. Part of the reason for this is that the models used by engineers when developing systems do not allow for emergent properties such as timing. This paper presents an approach and framework for addressing the problem of identifying an appropriate and valid set of timing requirements and their corresponding control parameters based on a combination of static analysis and simulation.

### **Timing Requirements & Control Attributes**

Bate, Nightingale & Cervin 2003

03/16/04

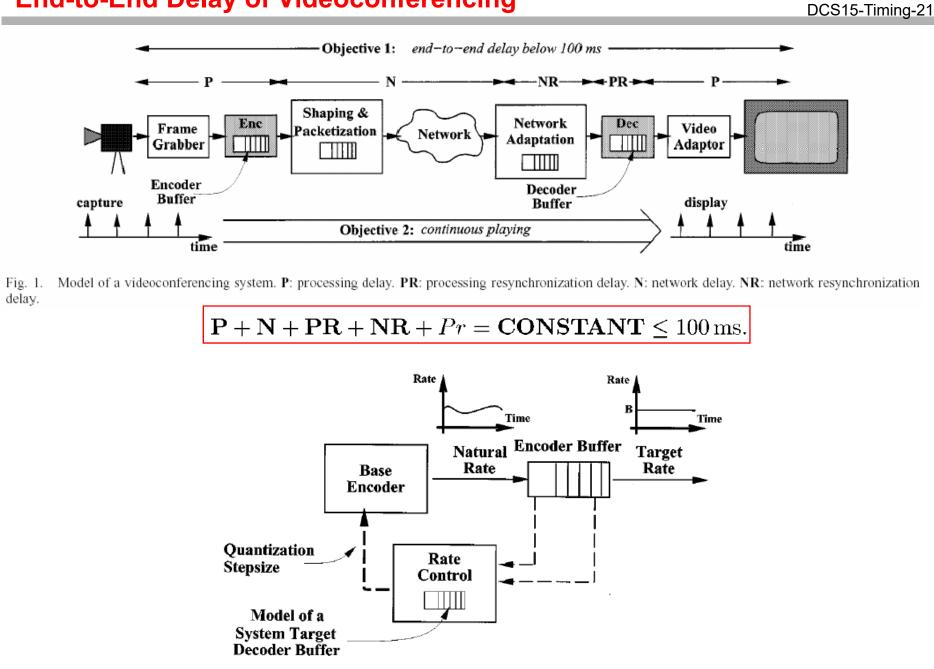

# End-to-End Delay of Videoconferencing

- M. Baldi and Y. Ofek,

- "End-to-end delay analysis of videoconferencing over packet-switched networks,"

- IEEE/ACM Transactions on Networking, 8(4): 479-492, Aug. 2000.

- Abstract (short):

- In order for the participants in a videoconference call to interact naturally, the end-to-end delay should be below human perception; even though an objective and unique figure cannot be set, 100 ms is widely recognized as the desired one-way delay requirement for interaction. Since the global propagation delay can be about 100 ms, the actual end-to-end delay budget available to the system designer (excluding propagation delay) can be no more than 10 ms. We identify the components of the end-to-end delay in various configurations with the objective of understanding how it can be kept below the desired 10ms bound. We analyze these components step-by-step through six system configurations obtained by combining three generic network architectures with two video encoding schemes. We study the transmission of raw video and variable bit rate (VBR) MPEG video encoding over 1) circuit switching; 2) synchronous packet switching; and 3) asynchronous packet switching. In addition, we show that constant bit rate (CBR) MPEG encoding delivers unacceptable delay—on the order of the group of pictures (GOP) time interval when maximizing quality for static scenes.

# End-to-End Delay of Videoconferencing

Baldi & Ofek 2000

03/16/04

Feng-Li Lian © 2021

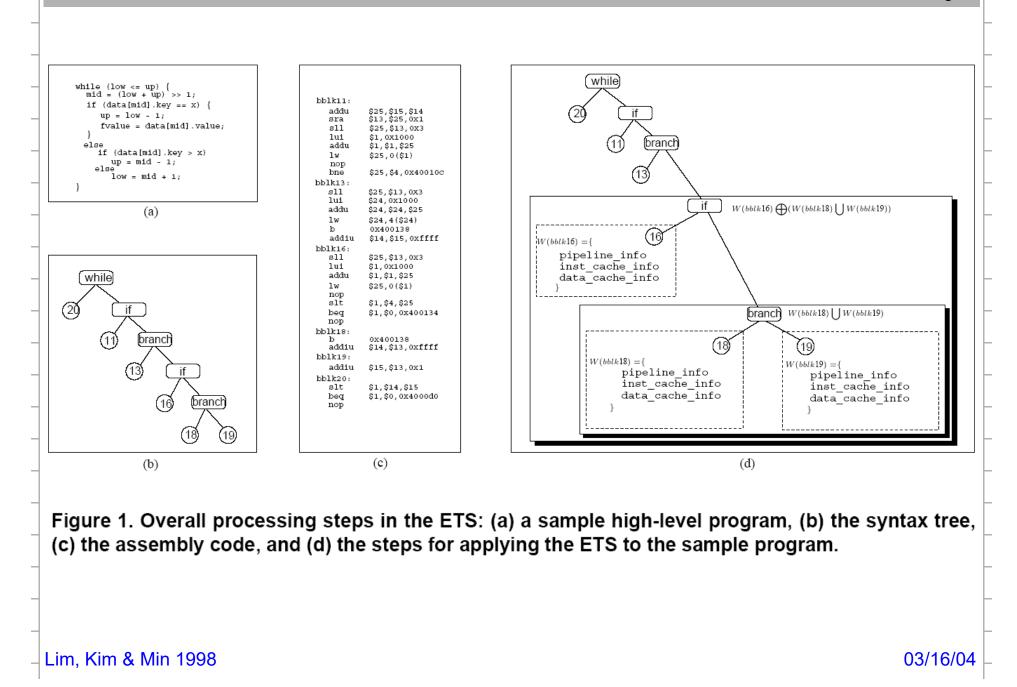

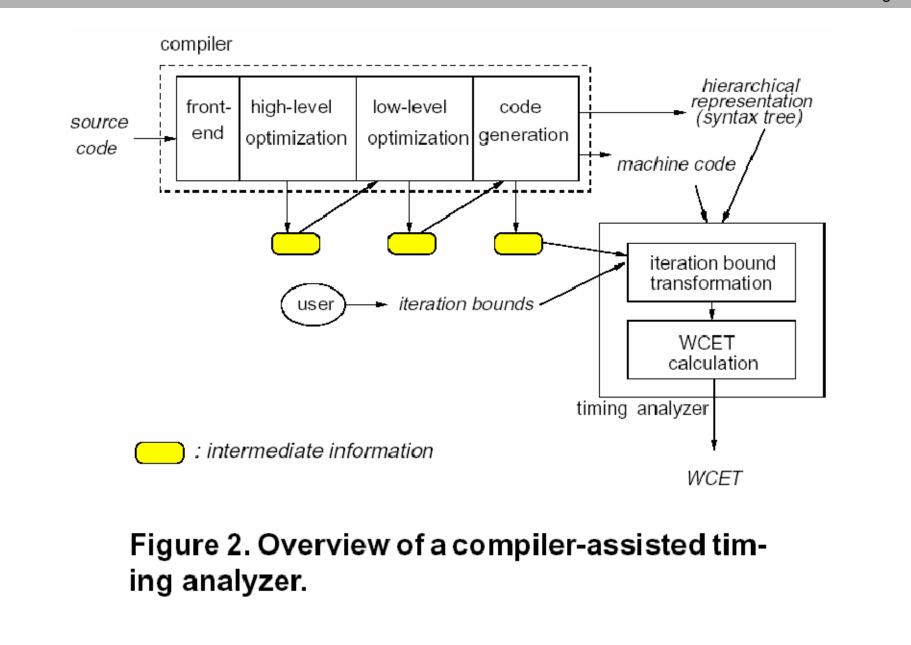

#### **Timing Analysis for Programs**

## Paper:

- S.-S. Lim, J. Kim, and S.L. Min,

- "A worst case timing analysis technique for optimized programs,"

- In Proc. Fifth Int'l Conf. Real-Time Computing Systems and Applications, pp. 151-157, Oct. 1998.

## Abstract:

We propose a technique to analyze the worst case execution times (WCETs) of optimized programs. Our work is based on a hierarchical timing analysis technique called the extended timing schema (ETS). A major hurdle in applying the ETS to optimized programs is the lack of correspondences in the control structure between the optimized machine code to be analyzed and the original source program written in a high-level programming language. We suggest a compiler-assisted approach where a timing analyzer relies on an optimizing compiler for a consistent hierarchical representation and an accurate sourcelevel correspondence that are essential for accurate WCET analysis for optimized programs. In order to validate the proposed approach, we implemented a proof-of-concept version of a timing analyzer for a 256-bit VLIW processor and compared the analysis results with the simulation results. The experimental results show that the proposed solution can accurately predict the WCETs of highly-optimized VLIW programs.

05/03/09

# **Timing Analysis for Programs**

# **Timing Analysis for Programs**

03/16/04

| Benchmark<br>Programs | Description                                                                |

|-----------------------|----------------------------------------------------------------------------|

| MatMul                | multiplies two 5 $\times$ 5 integer matrices                               |

| JFDCTINT              | performs the forward Discrete Cosine Transform<br>used in JPEG             |

| FIR                   | performs a 32-taps Finite Impulse Response (FIR)<br>filtering operation    |

| FFT                   | performs the Fast Fourier Transform (FFT) on<br>256 floating point numbers |

#### Table 1. The benchmarks used for the experiments.

| Benchmark<br>Programs | Simulation<br>Results | Analysis<br>Results |

|-----------------------|-----------------------|---------------------|

| MatMul                | 1673                  | 1739                |

| JFDCTINT              | 4456                  | 4780                |

| FIR                   | 30940                 | 32218               |

| FFT                   | 2879360               | 4567872             |

#### TMS320C6201

Table 2. Predicted and measured execution cycles of the benchmark programs.

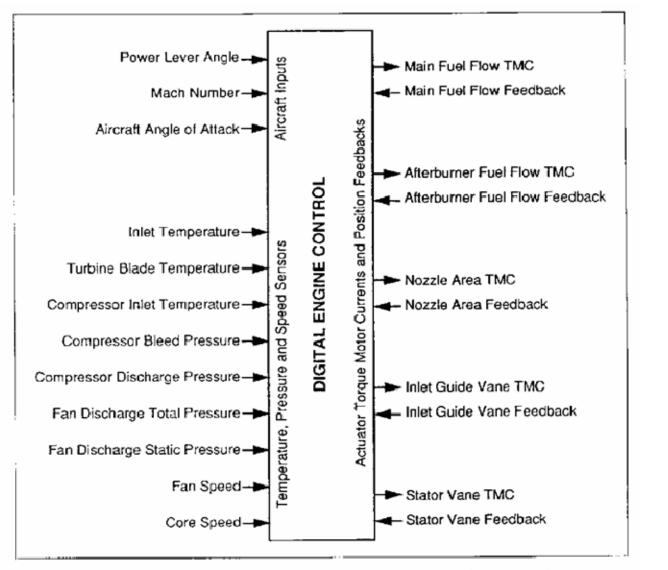

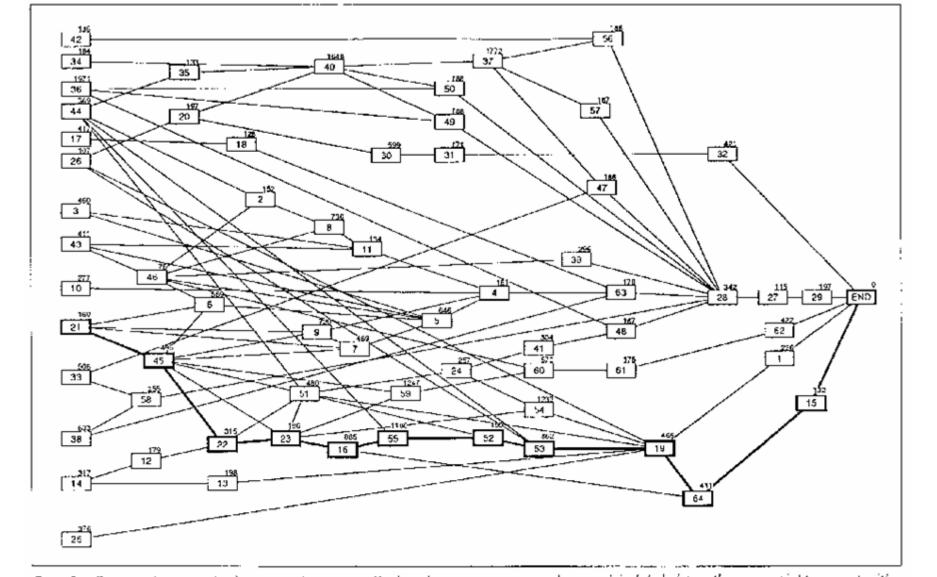

- P.L. Shaffer,

- "A multiprocessor implementation of real-time control for a turbojet engine,"

- IEEE Control Systems Magazine, 10(4): 38-42, June 1990.

- Abstract:

- A real-time control program for a turbojet engine has been implemented on a fourprocessor computer, achieving a speedup of 3.38 times the speed of a sequential version of the same program on a single processor. The concurrent program was produced from a sequential program by subjecting the sequential program to global, hierarchical interprocedural data-flow analysis and timing measurements. A static schedule for the constituent tasks of the control program on the four processors was determined using a heuristic algorithm based on the critical-path method. The approach should be applicable to a variety of control and related programs where iterative tasks with well-bounded execution times are computed in systems with hard real-time requirements.

Fig. 1. Digital engine control for a turbojet engine, showing inputs from aircraft, sensor inputs from engine, and actuator torque motor concurrent (TMC) outputs and position feedbacks.

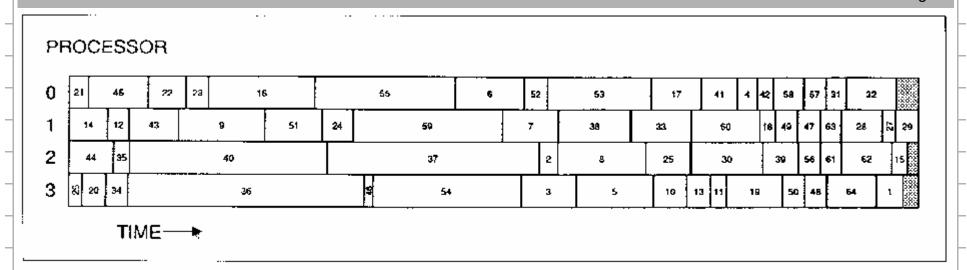

Shaffer 1990

Feng-Li Lian © 2021 DCS15-Timing-28

Fig. 2. Computation graph for control program. Each node represents a procedure, and is labeled (on the upper right corner) with the maximum execution time (ps). Graph edges represent data dependencies between routines (data flow is from left to right). External inputs and outputs are not shown.

Shaffer 1990

03/16/04

Feng-Li Lian © 2021 DCS15-Timing-29

Fig. 3. A possible schedule for the control program on four processors, representing a speedup of 3.94. The shaded areas represent idle processor time.

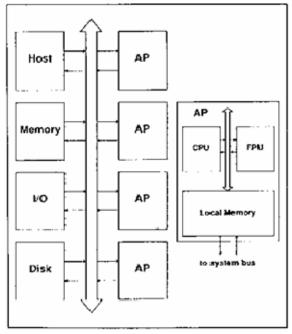

Fig. 4. The multiprocessor architecture used to implement the turbojet engine control program. Each application processor (AP) contains a 68020 central processor unit (CPU) and 68881 floating-point unit (FPU), as well as local RAM. The I/O (input/output) board is an Ethernet controller.

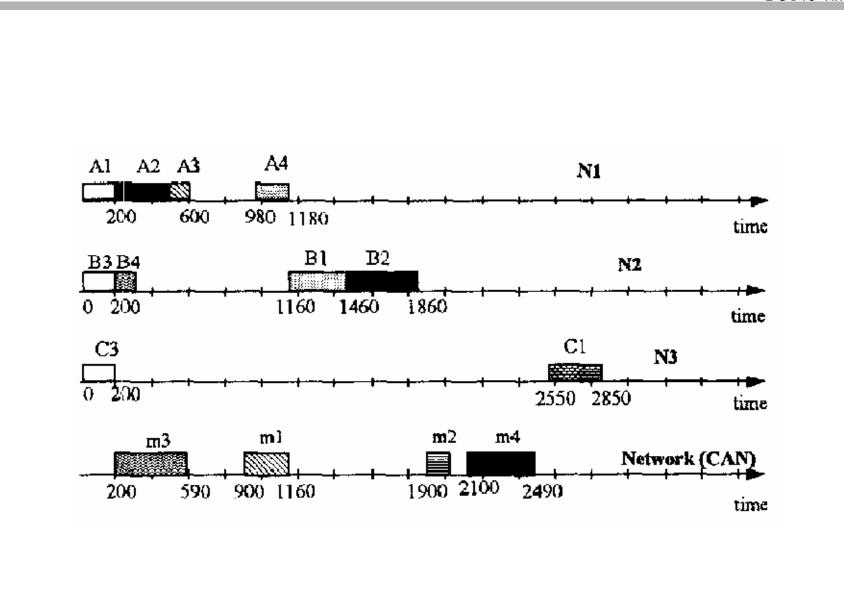

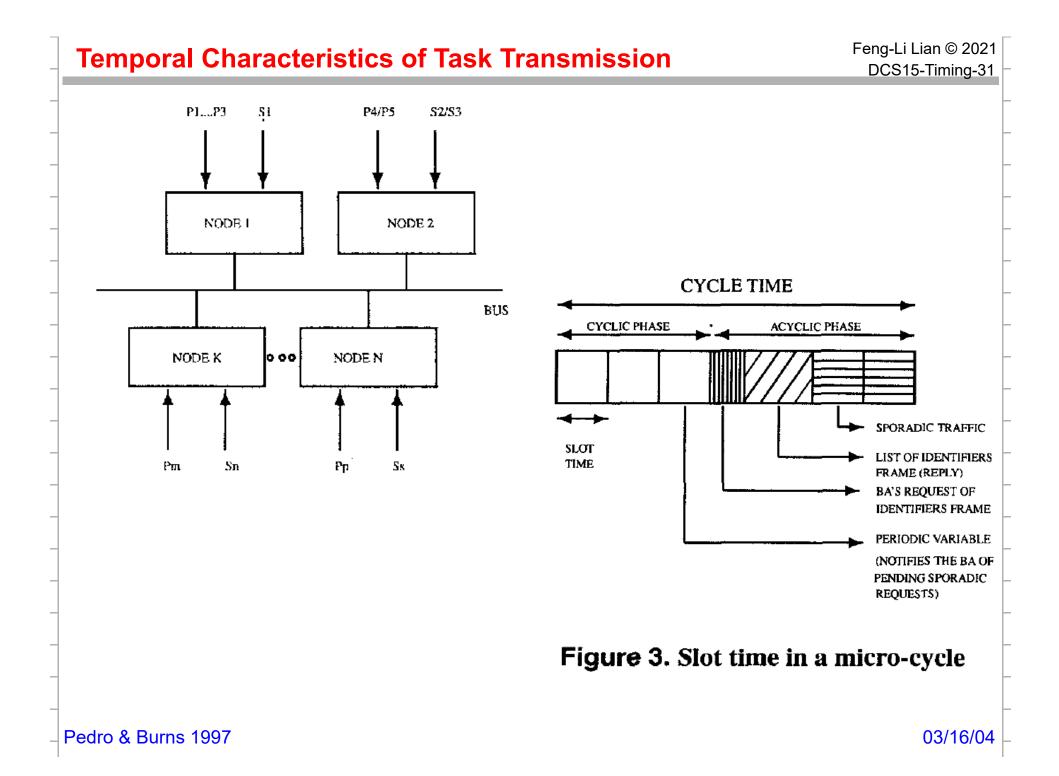

### **Temporal Characteristics of Task Transmission**

- P. Pedro and A. Burns,

- "Worst case response time analysis of hard real-time sporadic traffic in FIP networks,"

- Proc. Ninth Euromicro Workshop on Real-Time Systems, pp. 3-10, June 1997

- Abstract:

- Real-time fieldbuses are currently a significant issue in both process control and manufacturing areas. They constitute the base upon which real-time fault-tolerant distributed systems can be designed for these application areas. A potential large leap towards the use of Fieldbus in such time-critical applications lies in the evaluation of its temporal behaviour. In particular an important problem associated with the Fieldbus FIP is its inability to guarantee the timing performance of sporadic traffic. In this paper we develop the pre-run-time schedulability analysis of FIP bounding the worst case response time of the sporadic traffic

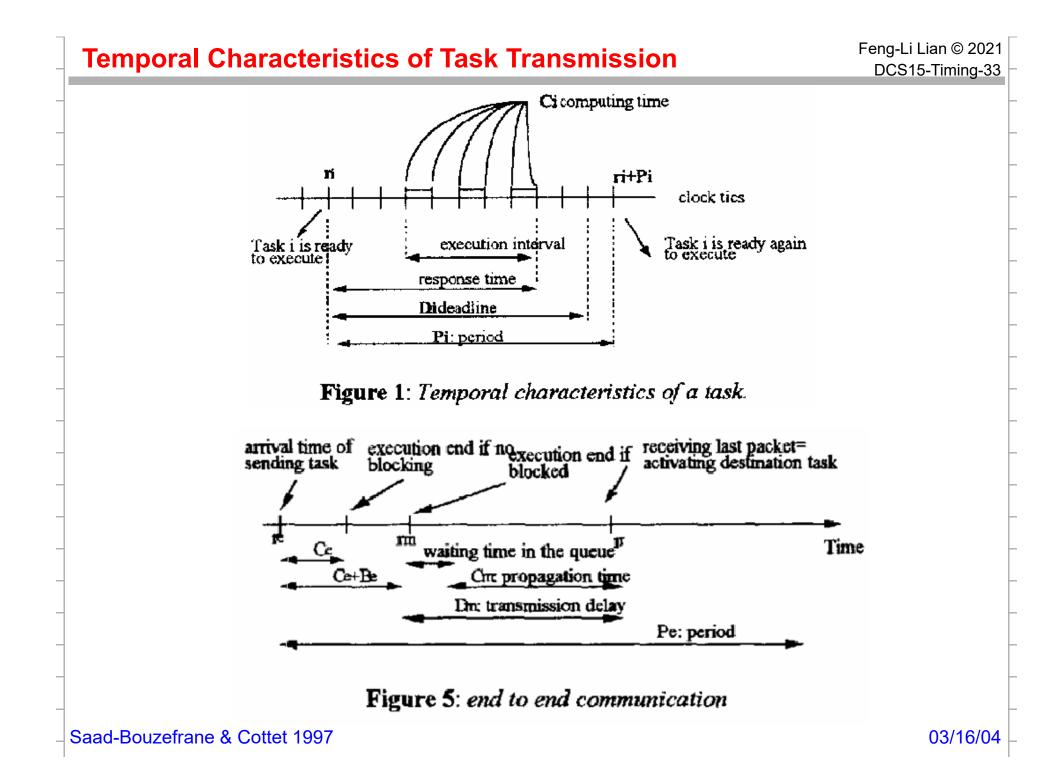

- S. Saad-Bouzefrane, and F. Cottet,

- "A performance analysis of distributed hard-real time applications,"

- Proc. IEEE Int'l Workshop on Factory Communication Systems, pp. 167-176, Oct. 1997

- Abstract:

- In distributed hard real-time applications there is a need for temporal analysis to evaluate and optimise a design with respect to the deadlines. The key method is the scheduling analysis of such applications, which means the schedulability not only of its tasks but of its messages too. The authors present a schedulability analysis which allows one to determine the timing parameters of messages and to update those of tasks. Given an initial task set characterised by temporal attributes and network interactions, this methodology permits one to produce valid execution sequences and to evaluate the relevant timing factors. Simulation results done with CAN and FDDI protocols are deduced.

Feng-Li Lian © 2021 DCS15-Timing-34

P

10000

20000

5000

15000

N2

**B2**

B4

#### **Temporal Characteristics of Task Transmission**

| Task               | node             | С          | P=D                    | plication tas<br>Pr | N1                    |                         |                        |                                   |                             |                                 |   |

|--------------------|------------------|------------|------------------------|---------------------|-----------------------|-------------------------|------------------------|-----------------------------------|-----------------------------|---------------------------------|---|

| $\overline{A_{l}}$ | NI               | 200        | 10000                  | 3                   | A1 -                  | - A2                    |                        | m1(2p)                            |                             |                                 |   |

| $A_2$              | NI               | 300        | 10000                  | 2                   |                       |                         | °                      |                                   | /•                          | ► B1                            |   |

| A3                 | $\tilde{N_I}$    | 100        | 20000                  | 1                   | A3                    | A4 🚽                    | •/                     | m3(3p)                            |                             | — B3                            | в |

| $A_4$              | NI               | 200        | 5000                   | 4                   |                       | $\leftarrow$            |                        | 110(5p)                           |                             | $\checkmark$                    | 2 |

| $B_I$              | $N_2$            | 300        | 10000                  | 2                   |                       | $\mathbf{X}$            |                        |                                   |                             |                                 |   |

| $B_2$              | $N_2$            | 400        | 10000                  | 1                   | 1                     | n2(1p)                  | $\backslash$           |                                   | m                           | 4(3p)                           |   |

| $B_3$              | $N_2$            | 200        | 5000                   | 3                   |                       |                         | X                      |                                   | X                           |                                 |   |

| B4                 | $N_2$            | 100        | 15000                  | 1                   |                       |                         | ( <b>`</b> cı          | C2                                | )                           |                                 |   |

| _                  |                  |            |                        |                     |                       |                         | <u>۱</u>               |                                   | / N3                        |                                 |   |

| $C_I$              | N3               | 300        | 20000                  | 2                   |                       |                         |                        | C3                                |                             |                                 |   |

| $C_{I}$<br>$C_{2}$ | N3<br>N3         | 300<br>150 | 20000<br>15000         | 2<br>3              |                       |                         |                        | C3                                | / 110                       |                                 |   |

| -                  |                  |            |                        |                     |                       |                         |                        |                                   |                             |                                 |   |

| C2                 | N3               | 150        | 15000                  | 3                   | T                     | able2                   |                        | C3                                |                             |                                 | s |

| C2                 | N3               | 150        | 15000                  | 3                   |                       |                         | CAN                    | ning attri                        | butes of                    | FDDI                            | 5 |

| C2                 | N3               | 150        | 15000                  | 3                   | message               | C                       | CAN<br>D               | ning attri                        | butes of                    | FDDI<br>D                       | s |

| C2                 | N3               | 150        | 15000                  | 3                   |                       |                         | CAN                    | ning attri                        | butes of                    | FDDI                            | s |

| C2<br>C3           | N3<br>N3         | 150<br>200 | 15000<br>10000         | 3 4                 | message               | <u>с</u><br>26          | CAN<br>D               | ning attri                        | butes of                    | FDDI<br>D                       | S |

| C2<br>C3           | N3<br>N3<br>m1 m | 150<br>200 | 15000<br>10000<br>n3 m | 3<br>4<br>4         | message<br>m1<br>— m2 | C<br>26<br>0<br>13<br>0 | CAN<br>D<br>260<br>650 | ming attri<br>P<br>10000<br>20000 | butes of<br>C<br>726<br>363 | FDDI   D   3726   6726          | s |

| C2<br>C3           | N3<br>N3<br>m1 m | 150<br>200 | 15000<br>10000<br>n3 m | 3 4                 | message<br>m]         | C<br>26<br>0<br>13      | CAN<br>D<br>260        | ming attri<br>P<br>10000          | butes of<br>C<br>726        | <b>FDDI</b><br><b>D</b><br>3726 | s |

Saad-Bouzefrane & Cottet 1997

03/21/05

#### **Temporal Characteristics of Task Transmission**